FPGA Filter Implementation Overview

I assisted one of my fellow graduate students in some directed research she was doing on FPGA filter implementation. She was tasked with understanding and realizing several types of filters on FPGA hardware. All the filters designed were 15th order flters and used 16-bit fixed point math. The performance and resource usage of the filters was then examined. Her final presentation on her research can be viewed below:

FPGA Filter Implementation Presentation FPGA Filter Implementation RepositoryFIR Filter

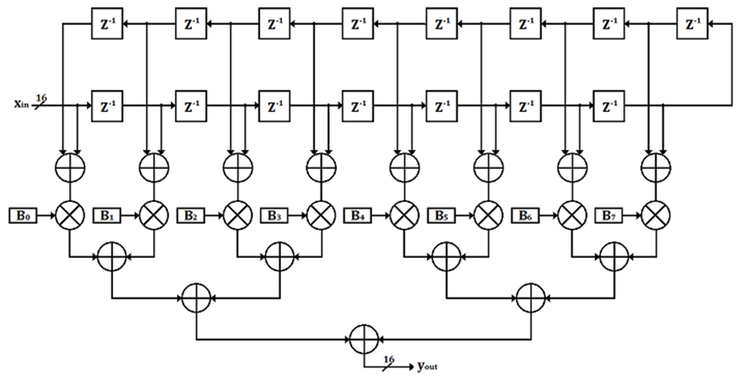

The FIR filter is the simplest and fastest of the four filters. It takes advantage of symmetry with the use of pre-adders. Also, an adder tree was used to minimize the combinational path delay.

FIR Filter Source

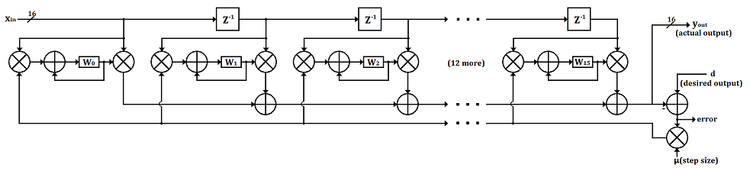

Least Mean Squared (LMS) Filter

The LMS adaptive filter completes its output calculations and weight updates in a single clock cycle. Because of its single cycle operation, extensive combinational delays are present. This filter can only run at a fraction of the speed of the FIR filter.

LMS Filter Source

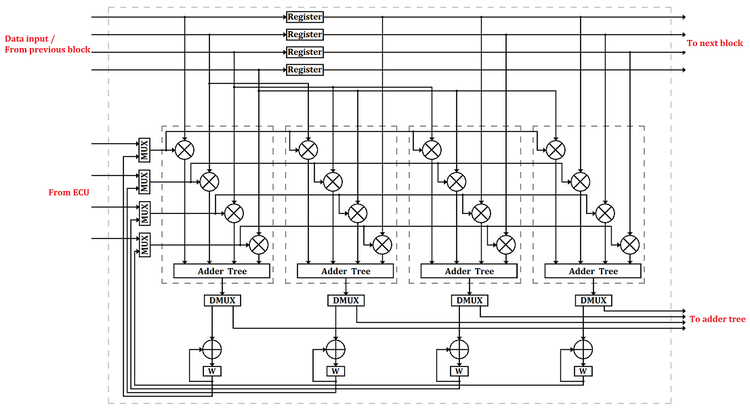

Block FIR Filter

The block FIR filter was created as an initial test of the block concept as its compute blocks are much simpler than the LMS filter compute blocks. The core of the filter is composed of four compute blocks and operates on four data samples per clock cycle.

Block FIR Filter Source

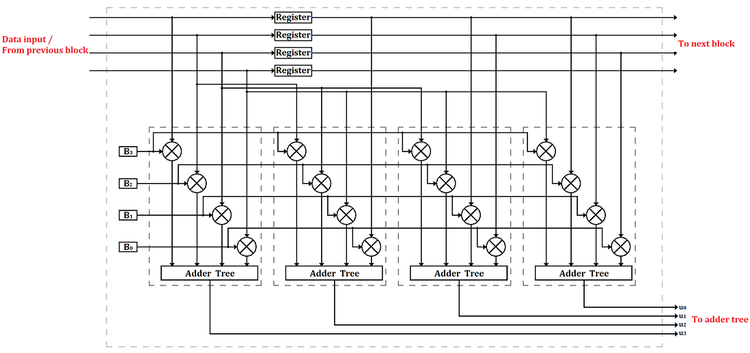

Block LMS Filter

The final and most complicated filter is the Block LMS filter. It also has four compute blocks and can operate on four data samples at a time but it has a simple state machine that breaks its operations into two clock cycles. One clock cycle computes the output value while the other clock cycle updates the weights.

Block LMS Filter Source