Direct Digital Synthesizer Overview

The DDS was to be designed with the following parameters:

1. The DDS is to generate samples at a sample rate of 245.76MHz

2. The FPGA clock frequency is 245.76MHz

3. A phase truncation architecture is to be employed

4. The DDS trig look-up table is to be realized in FPGA block memory (BRAM)

5. 4-fold symmetry will be used (only store 1/4 of a cycle) to

minimize the number of BRAMs used in the design

6. The DDS will be tuned to 2 different frequencies: 10:457MHz and 80:957MHz

Two solutions were tested:

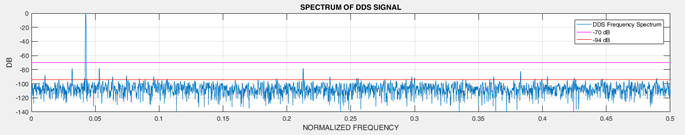

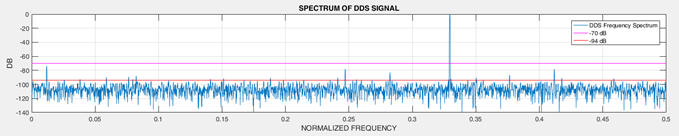

1. Spurious free dynamic range (SFDR) of at least -70dBc

2. SFDR of at least -94dBc

Vivado Design Files

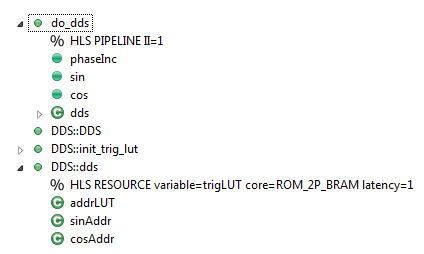

The DDS was designed in HLS. The following is the HLS source code:

Vivado Design FilesVivado Design Results

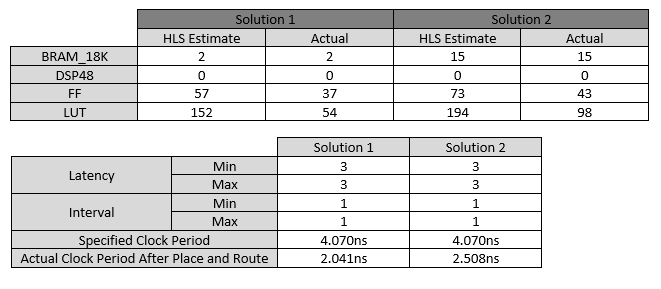

Next are the resource utilization and timing results for the solution:

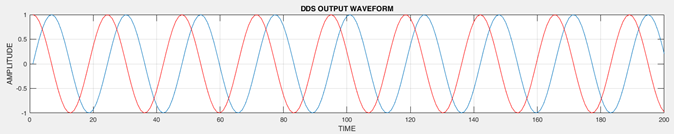

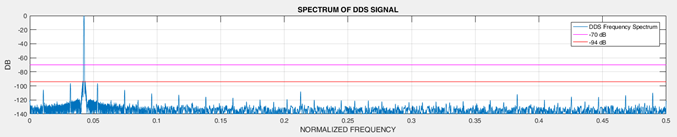

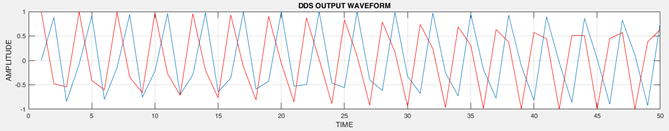

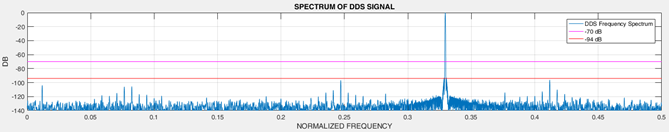

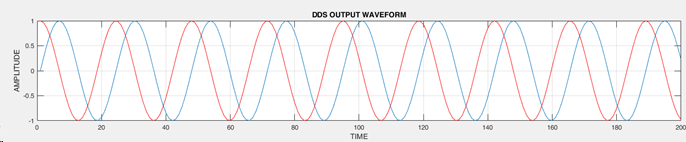

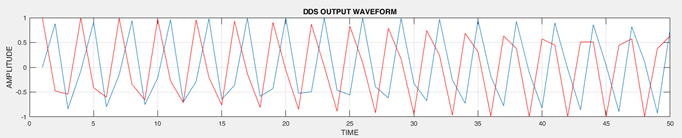

Matlab Analysis Plots

Solution 1 (SFDR of at least -70dBc)

Solution 2 (SFDR of at least -94dBc)